带真值表的半加法器和全加法器的说明

在组合电路中,不同的逻辑门用于设计编码器,多路复用器,解码器和解复用器。这些电路具有一些特征,如该电路的输出,主要取决于随时在输入端子处的级别。该电路不包括任何内存。输入的早期状态对该电路的当前状态没有任何影响。组合电路的输入和输出为“n”。输入和'M'没有。产出。一些组合电路是半加法器和全加法器,减法器,编码器,解码器,多路复用器和多路分解器。本文讨论了半加法器和完整加法器的概述,它与真理表一起使用。

什么是加法器?

加法者是一个数字逻辑电路在电子学中广泛用于数字的加法。在许多计算机和其他类型的处理器中,加法器甚至用于计算地址和相关活动,计算ALU中的表索引,甚至用于处理器的其他部分。它们可以为许多数字表示形式(如超过3或二进制编码的十进制)构建。加法器基本上分为两种类型:半加法器和全加法器。

什么是半加法器和完整的加法器电路?

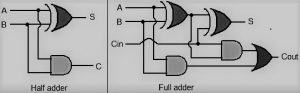

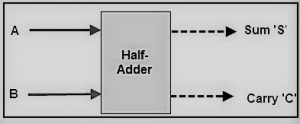

半加法器电路有两个输入:A和B,它们将两个输入数字相加,产生进位和和。全加法器电路有三个输入:A和C,它们将三个输入数相加,生成进位和和。这篇文章给出了关于半加法器的用途的详细信息和以表格形式甚至在电路图中的完整加法器。已经提到了加入者的主要和关键目的是添加的。以下是详细的半加法器和全加法器理论。

一半加法器

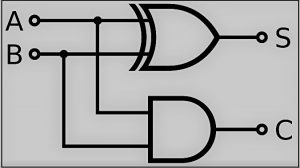

那么,在半加法器的情况下,它将两个二进制数字相加其中的输入位被称为加数和加数结果有两个输出一个是和,另一个是进位。为了执行求和运算,异或运算应用于两个输入,和门运算应用于两个输入以产生进位。

而在全加法器电路中,它将3个1位数字相加,其中2个位可以作为操作数,另一个被称为进位。产生的输出是2位输出,这些可以被称为输出进位和和。

通过使用半加法器,可以在逻辑门的帮助下设计简单的加法。

让我们看一下添加两个单位的示例。

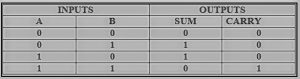

2比特的半加法器真值表如下:

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

这些是最不可能的单位组合。但是1 + 1的结果是10,必须将SUM结果重写为2位输出。因此,可以写入等式

0 + 0 = 00

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

输出'1'of'10'进行。“总和”是正常输出,“携带”是开关。

现在我们已经清楚了,使用输出“和”的异或门和“进位”的和门可以很容易地实现1位加法器。

例如,当我们需要在一起添加两个8位字节时,可以通过使用全加法器逻辑电路来实现它。当您想要添加一个二进制数字数量时,半加法器很有用。

开发二二进制加法器的一种方法是建立真值表并将其化简。当你要做一个三位数的加法器时,一半加法器的加法运算要执行两次。同样地,当你决定做一个四位加法器时,这个运算要再执行一次。有了这个理论,很明显实现是简单的,但是开发是一个需要时间的过程。

最简单的表达式使用exclusive OR函数:

Sum= A XOR B

进位= A和B

和用基本的And、OR和NOT表示的等价表达式:

和= A.B + A.B '

半加法器的VHDL代码

实体哈

Port (a:在STD_LOGIC;

B:在std_logic;

sha:输出STD_LOGIC;

cha: out STD_LOGIC);

结束公顷;

上述电路的结构行为为

开始

sha <= a xor b;

cha <= a and b;

最终行为

半加法器IC号码

半加法器的实现可以通过高速CMOS数字逻辑集成电路实现,如74HCxx系列,包括SN74HC08(7408)和SN74HC86(7486)。

一半加法器的局限性

将这些二进制加法器称为半加法器的主要原因是,没有范围来包含使用前面的位的进位。所以,这是一个主要的限制,曾经使用过的二进制加法器,特别是在实时的情况下,需要添加几个位。因此,使用全加法器可以克服这种限制。

完整的加法器

与半加法器相比,此加法器难以实现。

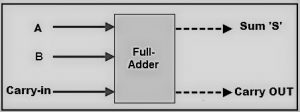

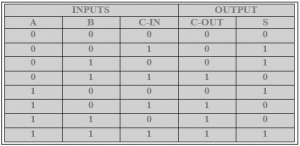

半加法器和全加法器之间的差异是全加法器有三个输入和两个输出,而半加法器只有两个输入和两个输出。前两个输入是A,第三个输入,第三输入是输入作为C-IN的输入。设计全加法器逻辑时,将八个集中在一起,以创建一个字节宽的加法器,并将携带位级联从一个加法器级联到下一个。

输出进位被指定为C-OUT,正常输出被表示为S,即' SUM '。

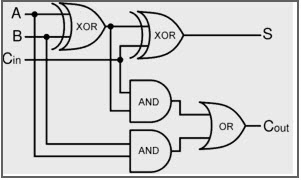

使用上面的全加器真值表说明:实现全加法器电路很容易理解。-S的和由两个步骤产生:

- 通过xoring提供的输入'a'和'b'

- 然后将A XOR B的结果与C-IN进行XOR

这将生成SUM和C-OUT,只有当三个输入中有两个是高的时,C-OUT才为真,那么C-OUT将是高的。因此,我们可以利用两个半加法器电路来实现一个全加法器电路。首先,半加法器将A和B相加以产生部分和,然后利用后半加法器逻辑将C-IN加到前半加法器产生的和中以得到最终的S输出。

如果任何半加法器逻辑产生携带,则会有输出携带。因此,C-OUT将是半加法器携带输出的一个或函数。看看下面显示的完整加法器电路的实现。

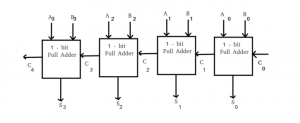

用上面的完整加法器逻辑实现更大的逻辑图是可能的,通常使用更简单的符号来表示操作。下面给出一个更简单的一位全加法器的原理图表示。

使用这种类型的符号,我们可以将两个位加在一起,从下一个较低的数量级取进位,并将一个进位发送到下一个较高的数量级。在计算机中,对于多位运算,每个位都必须用一个全加法器表示,并且必须同时加。因此,要相加两个8位数字,你需要8个完整的加法器,它可以由两个4位块级联而成。

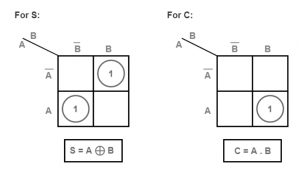

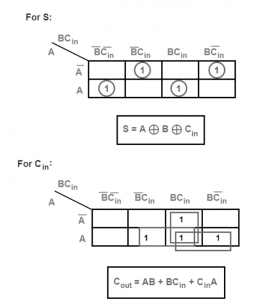

使用K-Map的半加法器和全加法器

即使是半加法器的总和和输出也可以通过Karnaugh地图(K-MAP)的方法获得。该半加法器和全加法器布尔表达式可以通过K-map得到。下面讨论这些加法器的k图。

半加法器K-MAP是

完整加法器K-Map为

逻辑表达和携带

求和的逻辑表达式可以根据表中提到的输入来确定。

= A ' B ' Cin + A ' B ' Cin + AB Cin

= Cin (A ' B ' + AB) + Cin (A ' B ' +A B ')

Cin EX-OR (A EX-OR B)

=(1、2、4、7)

进位(Cout)的逻辑表达式可以根据表中提到的输入确定。

= A ' b Cin + AB ' Cin + ABCin + ABCin

= AB + BCIN + ACIN

= (3, 5, 6, 7)

利用上述真值表,可以得到结果,其步骤为:

组合电路结合了电路中的不同门,其中可以是编码器,解码器,多路复用器、解复用器。组合电路的特点如下。

- 任何时刻的输出只基于输入端子处存在的级别。

- 它不使用任何内存。先前的输入状态对当前的电路状态没有任何影响。

- 它可以有任意数量的输入和m个输出。

VHDL编码

VHDL编码全加法器包括以下。

Entity full_add是

Port (a:在STD_LOGIC;

B:在std_logic;

CIN:在std_logic;

sum: out STD_LOGIC;

cout: out STD_LOGIC);

结束full_add;

full_add的体系结构行为是

组件哈

Port (a:在STD_LOGIC;

B:在std_logic;

sha:输出STD_LOGIC;

cha: out STD_LOGIC);

结束组件;

信号s_s,c1,c2: STD_LOGIC;

开始

HA1:哈端口映射(a, b, s_ (c1);

HA2:HA端口地图(S_S,CIN,SUM,C2);

cout<=c or c;

最终行为;

该半加法器与全加法器之差二分加法器产生结果全加法器使用二分加法器产生其他结果。类似地,当全加法器是两个半加法器时,全加法器是我们用来创建算术电路的实际块。

携带看法加入者

在纹波进位加法器电路的概念中,加法所需的位是立即可用的。而每个加法器段需要为前一个加法器块进位的到达保留时间。因此,当电路中的每个部分等待输入的到来时,需要更多的时间来产生和和进位。

例如,要发送第n个块的输出,它需要接收第(n-1)个块的输入。这种延迟被相应地称为传播延迟。

为了克服涟漪延迟携带加法器,介绍了一种携带看法加法器。这里,通过使用复杂的硬件,可以最小化传播延迟。下图显示了使用完整加法器的携带保护加法器。

真值表及相应的输出方程为

| 一种 | B. | C | C + 1 | 健康)状况 |

| 0. | 0. | 0. | 0. | 没有携带 生成 |

| 0. | 0. | 1 | 0. | |

| 0. | 1 | 0. | 0. | |

| 0. | 1 | 1 | 1 | 没有携带 传播 |

| 1 | 0. | 0. | 0. | |

| 1 | 0. | 1 | 1 | |

| 1 | 1 | 0. | 1 | 携带 生成 |

| 1 | 1 | 1 | 1 |

携带传播方程是pi = ai xor bi,并且携带产生是gi = ai * bi。利用这些等式,总和和携带方程可以表示为

SUM = PI XOR CI

Ci+1 = Gi + Ci *Ci

Gi只在不考虑输入进位的情况下,当输入Ai和Bi都为1时才提供进位。Pi与Ci到Ci+1的进位传播有关。

半加法器与全加法器之差

该半加法器和全加法器表的区别如下所示。

| 一半加法器 | 完整的加法器 |

| 半加法器(HA)是一种组合逻辑电路,用于实现两位个位数字的相加。 | 完整加法器(FA)是组合电路,此电路用于添加三位数字。 |

| 在HA中,一旦从以前的添加生成进位,就不能添加到下一步。 | 在FA中,一旦从前面的加法中生成进位,那么它就可以被添加到下一步。 |

| 半加法器包括两个逻辑门和栅极和门或门。 | 全加法器包括两个前或门、两个或门和两个与门。 |

| 半加法器的输入位是A, B。 | 全加法器的输入位有A、B和C-in三个 |

| 一半加法器和进位方程是 S = a⊕b;C = a * b |

全加法器逻辑表达式为 s =a¼b⊕cin;cout =(a * b)+(cin *(aəb))。 |

| HA用于计算机、计算器、用于数字测量的设备等。 | FA用于数字处理器、多比特加法等。 |

该半加法器和全加法器的关键区别在下面讨论。

- 半加法器通过两个二进制输入相加来生成和和进位,而全加法器则通过三个二进制输入相加来生成和和进位。半加法器和全加法器的硬件结构是不一样的。

- 区分HA和FA的主要特征是,在HA中没有这样的交易来考虑最后的添加carry,就像它的输入一样。但是,FA定位一个特定的输入列,比如Cin,来考虑最后一个加法的进位。

- 两个加法器将根据电路中使用的组件显示差异。半加加法器(HA)设计,其中两个逻辑门的组合如和&ex-ant,而FA的组合设计为三个和两个XOR&1或栅极的组合。

- 基本上,HA操作2- 2个1位的输入,而FA操作3个1位的输入。半加法器用于不同的电子设备中进行加法运算,而全加法器用于数字处理器中进行长位的加法运算。

- 这两种加法器的相似之处是,HA和FA都是组合数字电路,所以它们不使用任何存储器元素,如顺序电路。这些电路是实现二进制数相加的算术运算所必需的。

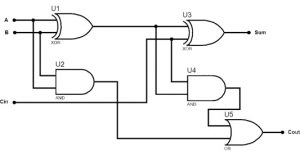

使用半加器的完整加法器实现

FA的实现可以通过逻辑连接的两个半加法器完成。下面可以如下所示的框图,它介绍了使用两个半加加法器的FA的连接。

前面计算的求和和进位方程是

s =一个'b'cin + a'bc'in + abcin

cout = ab + acin + bcin

求和方程可以写成。

Cin (A ' B ' + AB) + C ' in (A ' B ' + AB ')

所以,SUM = CIN ex-or(a ex-or b)

CIN(EX-OR B)+ C'in(A EX-or B)

Cin EX-OR (A EX-OR B)

Cout可以写成如下所示。

COUT = AB + ACin + BCin。

cout = ab + acin + bcin(a +̅a)

= ABCin + AB + ACin + A’BCin

= AB (1 + Cin) + ACin + A’B Cin

=一个b + acin + a'b cin

= ab + acin(b + b')+ a'b cin

= ABCin + AB + A ' BCin + A ' BCin

= AB (Cin + 1) + AB Cin + A’B Cin

= AB + AB ' Cin + A ' B Cin

= AB + Cin (AB ' + A ' b)

因此,cout = ab + cin(a ex-or b)

根据上述两个和和进位方程,可以通过两个有门和一个或门来实现FA电路。上面给出了带有两个半加法器的全加法器的电路图。

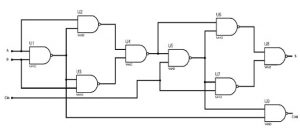

使用NAND Gates的完整加法器设计

与非门是一种通用门,用于执行任何类型的逻辑设计。带有与非门的FA电路图如下所示。

FA是一个简单的1位加法器,如果我们想执行n位加法器,那么n。在级联连接格式中必须使用1位的FAs。

优势

该半加法器和全加法器的优点包括以下。

- 半加法器的首要目的是把两个个位数相加

- 全加法器具有将前一个加的结果加一个进位的能力

- 通过完整的加法器,可以实现加法器,多路复用器等关键电路,以及许多其他可以实现

- 完整的加法器电路消耗最小功率

- 全加法器比半加法器的优点是:全加法器克服了半加法器的缺点;半加法器主要用于两个1位数相加。半加法器不加进位,因此采用了全加法器来克服这一缺点。在全加法器中,可以实现三位加法器并产生两个输出。

- 加法器的设计很简单,它是一个基本的构建块,因此可以很容易地理解一位加法。

- 这个加法器可以通过加一个逆变器转换成半减法器。

- 利用全加法器可以获得高的输出。

- 高速

- 非常强的供电电压缩放

缺点

该半加法器和完整加法器的缺点包括以下。

- 另外,半加法器在进位前不能使用,所以不适合级联多位相加。

- 为了克服这个缺点,FA必须添加三个1位。

- 一旦FA以像RA(纹波加法器)的链形式使用,则可以减小输出的驱动能力。

应用程序

半加法器和全加法器的应用如下。

- 添加二进制位可以通过计算机内的ALU进行半加法器,因为它使用加法器。

- 半加法器组合可以用来设计全加法器电路。

- 半添加剂用于计算器并测量地址以及表格

- 这些电路用于处理数字电路中的不同应用。在未来,它在数字电子中扮演着关键的角色。

- FA电路用作许多大电路中的元件,例如纹波携带加法器。此加法器同时添加位数。

- FAs用于算术逻辑单元(ALU)。

- FAs用于图形相关的应用程序,如GPU(图形处理单元)

- 它们用于乘法电路中执行乘法运算。

- 在计算机中,为了产生存储器地址和建立面向后续指令的程序对位,算术逻辑单元被使用全加法器。

因此,当两个二进制数相加时,两个数字首先相加的是最小位。这个过程可以通过半加法器执行,因为最简单的n/w允许两个1位数字相加。这个加法器的输入是二进制数字,而输出是和和进位C。

每当包括数字的数量时,那么HA网络即可仅用于连接最少的数字,因为HA无法从较早的类添加载位号码。完整加法器可以定义为所有数字算术设备的基础。这用于添加三位1位数字。该加法器包括三个输入,如A,B和CIN,而输出是SUM和COUT。

相关的概念

该与半加法器和全加法器相关的概念只是不要坚持一个单一的目标。它们在许多应用中有广泛的用途,并提到一些相关的:

- 半加法器和完整加法器IC号码

- 8位加法器的开发

- 半加法器的预防措施是什么?

- 一个波纹进位加法器的JAVA小程序

因此,这是关于半加法器和全加法器理论在给出真值表和逻辑图的同时,给出了半加法器全加法器电路的设计。的许多半加法器和全加法器PDF文档可以提供这些概念的高级信息。此外,知道这一点也很重要如何实现4位全额加法器?

很容易理解,谢谢,先生

hiiii

不错的

提供更多关于主题的信息

好的谢谢问

这个话题,之前我不能看到我没有得到充分的了解在每个网站…我同意了。

非常有趣的信息!完美的正是我所寻找的!

嗨

非常感谢您对我的文章的回复

如需任何协助,请电邮至team@elprocus.com.

哦,先生,这是一个很有趣的话题

嗨Payal

谢谢你的夸奖

如需任何协助,请电邮至team@elprocus.com.

哦,先生,这对我太好了

伟大的作品和伟大的知识....

谢谢

这是一篇非常有趣和有用的文章。谢谢你的分享。

thnx先生,它是可以理解的

请告诉我半加法器和满加法器的特点

以及在日常生活中使用蝮蛇

谢谢先生

谢谢你,先生

这是惊人的先生...... ..

真的可以理解

谢谢你先生

谢谢你,先生

我们如何在NAND或NOR门的帮助下制作半加法器和完整加法器......

先生请回复..

谢谢

先生

干得好,先生,非常感谢

磨坊主