脉冲产生的重要多谐振荡器电路是什么?

多振子电路是指特殊的电子电路类型用于产生脉冲信号。这些脉冲信号可以是矩形或方波信号。它们的产出通常有两种状态:高或低。多谐振荡器的一个特殊特性是使用无源元件如电阻和电容来确定输出状态。

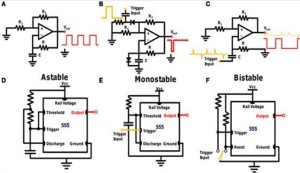

类型的Multi-Vibrators

一个。单稳态Multi-vibrator:单稳态多谐振荡器是指输出只处于一种稳定状态的多谐振荡器电路。它也被称为一次性多谐振荡器。在单稳态多谐振荡器中,输出脉冲持续时间由RC时间常数决定,给定为:1.11*R*C

b。一个稳定的Multi-vibrator:稳定振子是输出振荡的电路。它不需要任何外部触发,没有稳定状态。它是一种再生振荡器。

c。双稳态Multi-vibrator:双稳振子是一种具有高、低两种稳定状态的电路。通常需要一个开关在输出的高电平和低电平之间切换。

三种多振子电路

1.使用晶体管

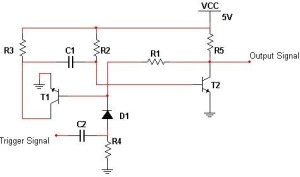

一。单稳态Multi-vibrator

在上述电路中,在没有任何外部触发信号的情况下,晶体管T1基极处于地电平,集电极处于较高的电位。而晶体管T2的基部通过电阻从VCC得到正电压供应,将晶体管T2驱动到饱和状态。并且,当输出引脚通过T2连接到地面时,它处于逻辑低电平。

当触发信号作用于晶体管T1基极时,晶体管开始导电,因为基极电流增加。当晶体管导通时,集电极电压降低。同时,电容C2的电压通过T1开始放电。这导致T2的基极电位下降,最终T2被切断。由于输出引脚现在通过电阻直接连接到一个正电源:Vout是在逻辑高电平。

一段时间后,当电容器完全放电,它开始通过电阻器充电。晶体管T2基极处的电势开始逐渐增大,最终被导通。因此,输出再次处于逻辑低电平或电路回到其稳定状态。

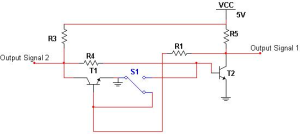

b。双稳态多谐振荡器

上述电路为双稳态多谐电路,有两个输出,定义了电路的两种稳定状态。

首先,当开关在A位置时,晶体管T1基极处于地电位,因此晶体管T1被切断。同时,晶体管T2基极处于较高电位,晶体管开始导电。这使得输出引脚1直接连接到地,Vout1处于逻辑低电平。T1的集电极的输出pin2直接连接到Vcc, Vout2处于逻辑高电平。

现在,当开关在B位置时,晶体管动作被逆转(T1导电,T2切断),输出状态被逆转。

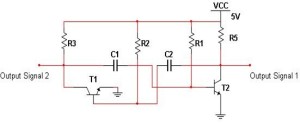

c。不稳多谐振荡器

上述电路为振荡电路。假设晶体管T1导通,T2截止,输出2为逻辑电平,输出1为逻辑低电平。当电容c2开始通过R4充电时,T2基部的电势开始逐渐增大,直到T2开始导电。这会降低它的集电极电势,并且T1基部的电势逐渐减小,直到它完全被切断。

现在,当C1通过R1充电时,晶体管T1基部的电势开始增加,最终被驱动传导,整个过程重复。因此,输出是不断重复或振荡的。

除了使用BJTs,其他类型的晶体管也用于多振子电路。

2.使用逻辑门

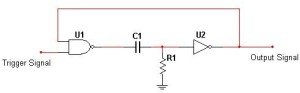

一。Mono-Stable Multi-Vibrator

最初电阻器上的电势在地平面上。这意味着一个低逻辑信号到非门的输入。因此,输出是在逻辑高电平。

由于与非门的输入均处于逻辑高电平,输出为逻辑低电平,电路输出保持稳定状态。

现在,假设一个逻辑低信号给与非门的一个输入,另一个输入在逻辑高电平,门的输出是逻辑1,即正电压。由于在R上有电位差,VR1处于逻辑高电平,因此非门的输出为逻辑0。当这个逻辑低信号被反馈到与非门的输入时,它的输出保持在逻辑1,电容电压开始逐渐增加。这反过来导致电阻器上的电位下降,即,VR1开始逐渐减少,在某一点上它变得低,这样一个逻辑低信号被馈送到非门的输入,而输出又是在逻辑高信号。输出保持稳定状态的时间周期由RC时间常数决定。

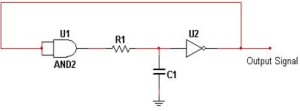

b。不稳Multi-vibrator

最初,当电源给定时,电容器是不带电的,一个逻辑低信号被馈送到非门的输入端。这使得输出在逻辑高电平。当这个逻辑高信号被反馈到和门,它的输出是在逻辑1。电容器开始充电,非门的输入电平增加,直到它达到逻辑高阈值,而输出是在逻辑低。

再次,和门输出是在逻辑低(逻辑低输入被反馈),电容器开始放电,直到它的电位在非门输入达到逻辑低阈值,输出再次被切换回逻辑高。

这实际上是一种张弛振荡器电路。

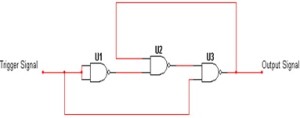

c。双稳态Multi-vibrator

双稳态多谐振荡器的最简单形式是由逻辑门实现的SR锁存器。

假设初始输出为逻辑高电平(Set),而输入触发信号为逻辑低电平(Reset)。这使得与非门1的输出处于逻辑高电平。由于U2的两个输入都是逻辑高电平,所以输出都是逻辑低电平。

由于U3的两个输入都处于逻辑高电平,所以输出处于逻辑低电平,即复位。同样的操作也发生在输入端的逻辑高信号上,电路在0和1之间改变状态。如所见,多振子逻辑门的使用实际上是数字逻辑电路的例子。

3.使用555定时器

555定时集成电路最常用的IC是脉冲产生,尤其是脉冲宽度调制,用于多谐振荡器电路。

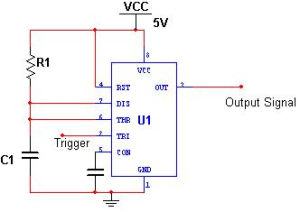

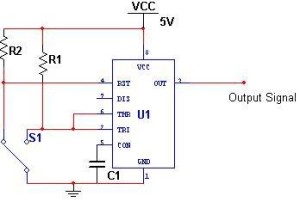

一。单稳态Multi-vibrator

要在单稳态模式下连接555定时器,在放电管脚7和地之间连接一个放电电容。产生的输出脉冲宽度由放电引脚、Vcc和电容C之间的电阻R的值决定。

如果你知道555定时器的内部电路,你必须知道a555定时器的作品一个晶体管,两个比较器和一个SR触发器。

最初,当输出处于逻辑低信号时,晶体管T被驱动到导通,引脚7被接地。假设一个逻辑低信号被应用到触发输入端或比较器输入端,由于这个电压小于1/3Vcc,比较器IC的输出就会变高,导致触发器复位,这样输出就会处于逻辑低电平。

同时,晶体管被关闭,电容器开始通过Vcc充电。当电容器电压增加到2/ 3vcc以上时,比较器2的输出变高,导致SR触发器被设置。因此,根据R和C的值,经过一段时间后,输出再次回到稳定状态。

b。不稳多谐振荡器

要在不稳定模式下连接555定时器,引脚2和6缩短,电阻连接引脚6和7之间。

最初,假设SR触发器的输出处于逻辑低电平。这关闭晶体管和电容开始充电Vcc通过Ra和Rb这样的方式,在一个时间,比较器2的输入电压超过阈值电压2/ 3vcc,比较器输出高。这导致SR触发器以这样一种方式设置计时器输出在逻辑低。

现在,晶体管被基极的逻辑高信号驱动到饱和状态。电容通过Rb开始放电,当电容电压降至1/3 Vcc以下时,比较器C2的输出处于逻辑高电平。这将重置触发器,计时器输出再次在逻辑高电平。

双稳态Multi-vibrator c。

双稳态多谐振荡器555定时器不需要使用任何电容;而一个SPDT开关被用于接地和引脚2和4之间。

当开关位置使引脚2与引脚6同时接地时,比较器1的输出为逻辑低信号,而比较器2的输出为逻辑高信号。这将重置SR触发器,触发器的输出逻辑低。因此,定时器的输出是逻辑高信号。

当开关位置是这样一种方式,引脚4,或复位引脚的触发器接地,SR触发器被设置,并且输出在逻辑高。定时器的输出为逻辑低信号。因此,根据开关位置,可以得到高脉冲和低脉冲。

这些就是用来产生脉冲的基本多谐振荡器电路。我们希望你对多谐振荡器有一个清晰的认识。

这里有一个简单的问题给所有的读者:

除了多激振器外,用于脉冲产生的其他电路类型是什么?

我知道这个网页提供高质量的文章和其他信息,

有没有其他网站提供这类高质量的信息?

请我可以得到项目主题,说设计和实现一个不间断电源供应系统从你们的人。如果我能在gmail上看到我的详细信息

一个很棒的工作。inmoofatirn超级有帮助。