晶体管晶体管逻辑(TTL)

逻辑系列介绍:

像NAND等逻辑门,也不用于日常应用程序以执行逻辑操作。使用像BJT,二极管或FET等半导体器件制造的栅极。使用集成电路构造不同的门。根据特定电路技术或逻辑系列,根据特定电路技术或逻辑系列制造数字逻辑电路。

不同的逻辑系列是:

- RTL(电阻晶体管逻辑)

- DTL(二极管晶体管逻辑)

- TTL(晶体管晶体管逻辑)

- ECL(发射器耦合逻辑)

- CMOS(互补金属氧化物半导体逻辑)

在这些RTL和DTL中很少使用。

逻辑系列的功能:

- FAN OUT:负载数栅极的输出可以驱动而不会影响其通常的性能。通过LOAD,我们表示连接到给定门的输出的另一个栅极的输入所需的电流量。

- 功耗:它代表了设备所需的功率量。它是以mw测量的。它通常是电源电压的乘积和当输出高或低时绘制的平均电流量。

- 传播延迟:表示输入电平变化时经过的过渡时间。输出发生的延迟是使其转变的是传播延迟。

- 噪声裕度:表示输入允许的噪声电压量,不会影响标准输出。

TTL介绍:

它是一个完全由晶体管组成的逻辑家族。它采用具有多个发射器的晶体管。商业上它从744,74S86等开始的74系列。它是由James L Bui建造的1961年,并于1963年在逻辑设计中商业地使用

TTL分类:

TTLS根据输出分类。

1。开放收集器输出:主要特征是其输出为0时为0,当高时浮动。通常,可以应用外部VCC。

晶体管Q1表现为返回到后部的二极管群集。对于逻辑低电平的任何输入,相应的发射极限结是向前偏置的,并且Q1基部的电压降约为0.9V,对于晶体管Q2和Q3而言,不足以进行。因此,输出是浮动或VCC,即高水平。

类似地,当所有输入都很高时,Q1的所有基极交发电结都是反向偏置的,晶体管Q2和Q3获得足够的基极电流并处于饱和模式。输出处于逻辑低电平。(对于晶体管转到饱和,收集电流应大于基极电流的β倍)。

开路集电极输出的应用:

它用于3个主要应用:

- 在驱动灯或继电器

- 执行有线逻辑

- 在建造公共汽车系统

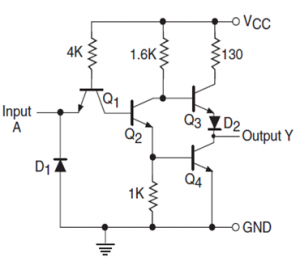

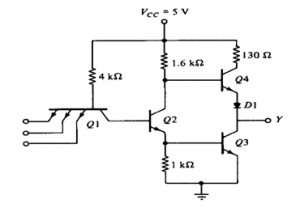

2.图腾杆输出:

图腾杆意味着在栅极的输出中添加电路的增加,这导致传播延迟的降低。

逻辑操作与开路收集器输出相同。晶体管Q4和二极管的使用是在Q3上提供寄生电容的快速充电和放电。电阻用于将输出电流保持为安全值。

3.三国家门:

它提供了3个状态输出。

- 当下晶体管接通时的低电平状态,上晶体管关闭。

- 较低晶体管关闭时的高电平状态,上晶体管接通。

- 两个晶体管关闭时的第三状态。它允许直线连接许多产出。

TTL系列的特点:

- 逻辑低电平为0或0.2V。

- 逻辑高级为5V。

- 典型的风扇为10。这意味着它可以在其输出端以最多10个门支持。

- 基本TTL设备绘制了几乎10MW的功率,这与使用肖特基设备减少。

- 平均传播延迟约为9ns。

- 噪声裕度约为0.4V。

TTL IC系列:

TTL IC主要从7系列开始。它有6个亚象征:

- 低功耗器件,具有35 ns的传播延迟和1mW的功耗。

- 低功耗肖特基设备延迟9ns

- 高级肖特基设备,延迟为1.5ns。

- 高级低功耗肖特基具有延迟4个NS和1MW的电源耗散的设备。

在任何TTL设备命名法中,前两个名称指示设备所属的子类的名称。前两位数字表示操作的温度范围。接下来的两个字母表指示子类所属的子类。最后两位数字表示芯片执行的逻辑功能。

例子是74LS02- 2既不输入也不是门。

74LS10-三重3输入NAND门。

TTL应用程序:

- 用于控制器应用程序,以提供0到5Vs

- 用作驱动灯和继电器的开关装置

- 用于处理器的迷你电脑像十二月vax.

- 用于打印机和视频显示终端

典型的TTL电路

逻辑门用于日常生活中的应用,如干衣机,电脑打印机,门铃等。

使用TTL逻辑实现的3个基本逻辑门如下: -

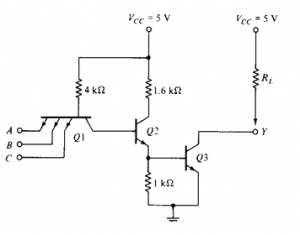

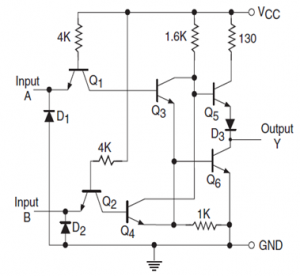

1.也没有门

假设输入A处于逻辑高电平,相应的晶体管的发射极基结是反向偏置的,并且基座集电极结是向前偏置的。晶体管Q3从电源电压Vcc获得基本电流并进入饱和度。由于来自Q3的低集电极电压,晶体管Q5将切断,另一方面,如果另一个输入低,则切断Q4并且相应地Q5通过晶体管Q3切断并输出直接连接到接地。同样,当两个输入都是低电平的逻辑,输出将处于逻辑高电平。

2.不是门

当输入低时,相应的基极 - 发射极结处于正向偏置,基本集电极结是反向偏置的。随着结果晶体管Q2被切断并且还切断晶体管Q4。晶体管Q3进入饱和度,二极管D2开始导通并且输出连接到VCC并进入逻辑高。同样,当输入处于逻辑高时,输出处于逻辑低电平。