什么是优先级编码器:工作及其应用

在数字电子学中,二进制编码器是多输入的组合逻辑电路,它同时考虑所有输入线,然后将它们转换为等效的单编码输出。n位数字编码器包含2 ^ n个输入线和n个输出线。克服二元的缺点编码器在美国,优先级编码器是基于最高优先级的输入而开发的。本文简要介绍了一种优先级编码器及其应用。

什么是优先编码器?

优先级编码器是一个组合逻辑电路,包含2 ^ n个输入线和n个输出线,并且表示所有输入线之间的最高优先级输入。当多个输入线同时为高电平时,首先考虑具有最高优先级的输入以生成输出。

它用于解决二进制编码器中多个高有功输入行产生错误输出的问题。如果同时有多个输入行是活动高电平(1),则该编码器对每个输入电平进行优先级排序,并为每个输入分配优先级。

此编码器的输出对应于具有最高优先级的输入。为了获得输出,只考虑优先级最高的输入,忽略所有其他输入行。这是一种二进制编码器或具有优先级功能的普通编码器。具有较大量级或最高优先级的输入优先编码,而不是其他输入行。因此,生成的输出基于分配给输入的优先级。

在大多数数字应用中,这些编码器用于选择具有最高优先级的输入。选择输入的过程称为仲裁。例如,当多个设备通过计算机系统发送数据时,该编码器使得具有最优先级的设备,并且允许访问所有其他设备中的计算机,其具有较低优先级。

这些编码器设计有4个输入和8个输入。4位优先编码器包含4个输入和2个输出以及一个有效输出。8位优先级编码器包含8个输入和3个输出。优先编码器电路与真值表为8位和4位解释在下一节。

8至3优先级编码器

这种编码器也被命名为二进制优先级编码器的8位或八进制。这种类型的编码器由8个输入和3个输出组成。当多个输入处于高处高电平的同时时,认为具有最高优先级的输入被认为表示输出。

例如,如果D1, D2和D3输入是有源高电平或逻辑1,而不管其他输入位,那么优先级编码器的编码输出将是D3 i, e111。这里,D1和D2输入位要么是无关的,要么是无关的。

8至3优先级编码器真理表如下所示。

D7 |

D6 | D5 | D4 | D3 | D2 | D1 | D0 | 一个 | B | C |

0 |

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

0 |

0 | 0 | 0 | 0 | 0 | 1 | X | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | X | X | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | X | X | X | 0 | 1 | 1 |

0 |

0 | 0 | 1 | X | X | X | X | 1 | 0 | 0 |

| 0 | 0 | 1 | X | X | X | X | X | 1 | 0 | 1 |

0 |

1 | X | X | X | X | X | X | 1 | 1 | 0 |

| 1 | X | X | X | X | X | X | X | 1 | 1 | 1 |

由上真值表可知,D0、D1、D2、D3、D4、D5、D6、D7为输入端,A、B、C为8 ~ 3优先级编码器的输出端。

优先级编码器的输出'A'仅在输入D4,D5,D6和D7处于高电平时表示为有效高或逻辑'1'。仅当输入D2,D3,D6和D7处于高电平的时,编码器的输出'B'仅在逻辑1处处于逻辑1。类似地,输出'C'仅当输入D1,D3,D5和D7处于高电平时才表示为逻辑'1'。

A、B、C的输出表达式由Karnaugh map (K-map)化简或真值表编写。

获得输出表达式如下所示,

A = D4 + D5 + D6 + D7

B = D2 + D3 + D6 + D7

C = D1 + D3 + D5 + D7

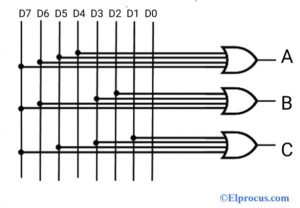

从这些简化的表达式,8到3的优先级编码器电路如下图所示,用逻辑门所示绘制图表。

标准IC 74LS148中有8至3种类型,由8个有效低或逻辑0输入和3个有效高或逻辑1输出位组成。这种类型的编码器的不同属性包括用于优先级编码的N位的级联,编码最优先级输入,代码转换,小数到BCD转换,当所有输入线都有高电平时,使能量低电平具有高电平的输出线。

4到2优先级编码器

这也被称为4位优先级,它由4个输入和2个输出线组成。因为编码器包含2^n的输入行和n个输出行。第三个输出是' V ',它被认为是一个有效的但指示器,当有多个输入行是高电平或活动(1)时,它被设置为1。

如果有效位等于'0',则所有输入都为'0'。在这种情况下,其他2个输出线被认为是不受'x表示的护理条件

的真理表4至2优先级编码器如下所示。

| D3 | D2 | D1 | D0 | 一个 | B | V |

0 |

0 | 0 | 0 | X | X | 0 |

1 |

0 | 0 | 0 | 0 | 0 | 1 |

X |

1 | 0 | 0 | 0 | 1 | 1 |

| X | X | 1 | 0 | 1 | 0 | 1 |

| X | X | X | 1 | 1 | 1 | 1 |

从上述真相表中,我们可以观察到D3,D2,D1,D0是输入;A和B是输出,V是有效位指示器。这里D3输入是最高优先级输入,D0是最低优先级输入。

当输入D3是有效的高(1),其具有最高优先级,而不管所有其他输入线,那么4位优先级编码器的输出为11。

当D3输入处于有效低电平并且D2是有效的,具有与所有其他输入线相关的下一个最高优先级,则输出为Ba = 10。

当D3、D2输入为低电平有功,D1为高电平有功,且不论剩余的输入线,D1优先级次之,则输出为BA = 01

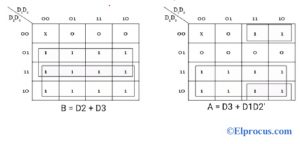

4位编码器的输出表达式可以通过卡诺映射(k映射)来确定,如下所示。

A = d3 + d1d2 '

B = D2 + D3

V = d0 + d1 + d2 + d3

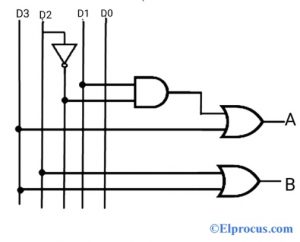

由上面的K-map可以得到输出A和B的简化表达式。从这些输出表达式中,4至2优先级编码器电路图说明与逻辑门如下所示。

的线路图4 - 2优先编码器与盖茨2或吸引,与门和非门的组合代表了有效,用于当多个输入逻辑(1)高。因此,四个输入和两个输出编码输入基于分配的优先级。

Verilog代码

当使用逻辑1分配多于一个输入线时,编码器的输出是不准确的。它仅在其中一个输入高(1)时才适用。因此,编码器不适用于多个高输入线。为了克服这一缺点,每个输入的级别优先考虑。因此,在多个输入线的情况下,编码器的输出对应于输入,其被指定为最优先级。这被称为优先级编码器。

在结构风格上优先级编码器Verilog代码如下所示。

模块or_gate (C, A, B);

输入A,B;

输出C;

指定C = | B;

末端;

模块not_gate(f,e);

输入E;

输出F;

分配f = -e;

末端;

模块And_gate(z,x,y);

输入x,y;

输出Z;

指定Z =用户;

末端;

模块优先级_encoder_struct(a0,a1,y0,y1,y2,y3);

输入Y0,Y1,Y2,Y3;

输出A0, A1;

not_gate u1(.f(y2bar),。e(y2));

and_gate u2(.z(w1),。x(y2bar),。y(y1));

or_gate(.c(a1),。a(y3),。b(y2));

or_gate (c (A0)。(日元)。B (W1));

末端;

编码器和优先级编码器之间的差异

编码器和优先编码器的主要区别是编码器产生一个错误输出时,多个输入是高的。但它们用于压缩数据的应用程序。因此,优先级编码器被引入,以克服问题二进制编码器。

优先级编码器通过考虑多个输入线之间的最高优先级输入来生成准确的输出。这些可以处理中断请求微处理器通过检测最高优先级的中断。

如果电路包含多个输入,则用于减少设计期间所需的电线数。

应用程序

某些优先级编码器的应用是谁,

- 它用于减少否。需要电线和连接电子电路设计具有多个输入线。示例键盘和键盘。

- 用于控制船舶导航中的位置和欧洲杯四强竞猜平台手臂的位置。

- 用于检测微处理器中断控制器的各种应用中的最高优先级输入。

- 用于通过通过网络传输二进制代码来保护来自黑客的整个网络。

- 用于对模数转换器的输出进行编码。

- 用于同步速度的同步。

- 二手机器人车辆

- 用于家居应用自动化系统与rf.

- 用于医院的健康监测系统

- 用于安全通信系统使用RF技术启用密码。

因此,这一切都是关于优先级编码器的概述定义,4至2&4至3优先级编码器电路图,8至3优先级编码器电路图,Verilog代码和应用程序。这是一个问题,“编码器和多路复用器之间的差异是什么?”