什么是完整的减法者:使用逻辑门的施工

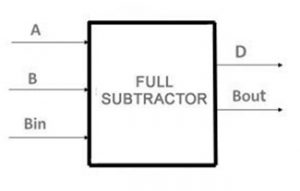

一般来说,全减法是最常用的减法之一基本组合逻辑电路。它是一种基本的电子设备,用于执行两个二进制数的减法。在早期的文章中,我们已经给了基本理论半加法器&全加法器它使用计算的二进制数字。同样,全减脚器使用二进制数字,如0,1的减法。这是电路可以用逻辑门构建,例如或,ex-or,nand门。该减法器的输入是A,B,Bin和输出是D,Bout。

本文给出了一个全减法的理论思想,包括什么是减法、用逻辑门设计、真值表等前提。这篇文章对于工程专业的学生来说是有用的,他们可以在HDL的实践实验室中研究这些主题。

什么是减法者?

二进制数字的减法可以借助减法电路来实现。这是一种组合逻辑电路,用于对两个二进制数字(如0和1)进行减法运算。二进制数字从0到0或0到1的减法不会改变结果,从1到1的减法会得到0,但从1到0的减法需要借位。

例如,双脚减法器电路包括两个输入,如A&B,而输出是差异和借用。该电路可以用加法器以及位于每个数据输入的逆变器以及FA的早期阶段的借用(BIN)输入之间构建。

减法器分为两种类型,如半部减法器和全减法器。在这里,我们正在讨论完整的减法者。

什么是完整的减法者?

它是一个电子设备或者逻辑电路它执行两位二进制数字的减法。它是数字电子设备中使用的组合逻辑电路。许多组合电路可用集成电路技术即加法器、编码器、解码器和多路复用器。在本文中,我们将讨论用半减法以及真值表等术语来构造它。

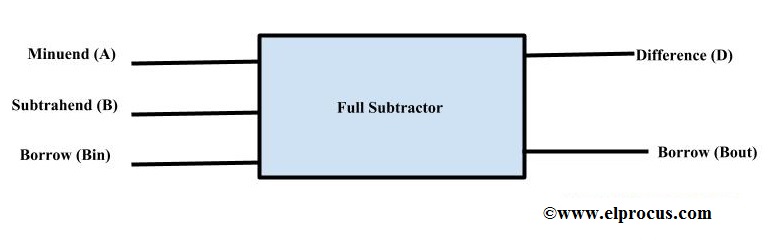

它的设计可以用两个半减法来实现,它涉及到三个输入,如减法、减法和借位,其中的借位是由两个二进制数字的减法得到的,并从下一个高阶位对中减去,输出为差和借位。

的完整的减法器块图如下所示。半减法器的最重要缺点是,我们不能在这个减法者中借用借款。虽然在其设计中,实际上我们可以在电路中借用借款,并可减去剩余的两个I / PS。这里是Minuend,B是subtrahend&bin借入。输出是差异(差异)和bout(借用)。完整的减法器电路可以通过使用具有额外或门的两个半减法器获得。

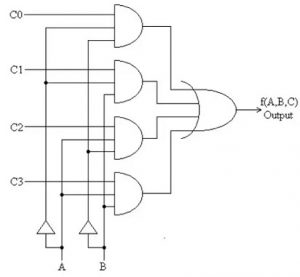

具有逻辑门的全减法器电路图

的使用基本门的全减法器电路图S在以下框图中示出。该电路可以用两个半减法器电路完成。

在初始半减法电路中,二进制输入是A和b。正如我们在之前的半减法文章中讨论过的,它将产生两个输出,即差分(Diff)和借位。

左减法器的差异O / P给出左半减法器电路。差异输出进一步提供给右半减法器电路的输入。我们在下一个其他I / P中提供了借款半减法器电路。再一次,它将给出差异,并借出钻头。该减法器的最终输出是差异输出。

另一方面,两种减法器电路中的借用连接到或逻辑门。晚些时候,除了给出两个输出位的给出或逻辑,我们会从减法器中获取最终借款。最后借用签署MSB(最重要的位)。

如果我们观察到这一点的内部电路,我们可以看到两个半个减法者,带有额外或门的NAND门和XOR门。

完整的减法器真相表

这减法器电路执行两个位之间的减法,它有3个输入(a、B和Bin)和两个输出(D和Bout)。这里的输入表示被减数、减数和前借数,而这两个输出表示借数o/p和差值。下图显示了全减法的真值表。

输入 |

输出 | |||

minuend(a) |

减数(B) | 借用(垃圾箱) | 差异(D) | 借用(Bout) |

0 |

0 | 0 | 0 | 0 |

0 |

0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 |

0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 |

1 | 0 | 0 | 0 |

1 |

1 | 1 | 1 | 1 |

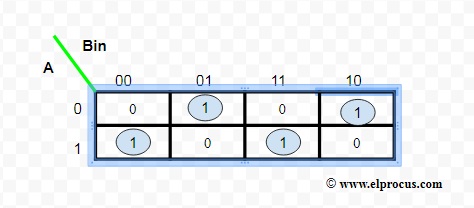

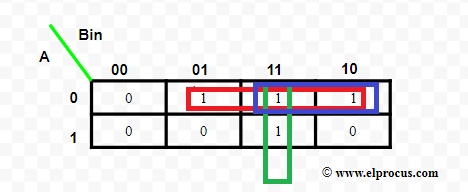

K-Map

的简化完整的减法器K-MAP对于上述差异而借阅如下所示。

下面提到了差异的等式以及箱。

差异的表达式是,

d = a'b'bin + ab'bin'+ a'bbin'+ abbin

借阅的表达是,

bout = a'bin + a'b + bbin

完整减法器电路的级联

在前面,我们已经讨论了类似结构的概述,电路图与逻辑门。但是如果我们想要减去两个其他的1位数字,这个减法电路是非常有用的单位数字级联,也可以减去两个以上的二进制数字。在这种情况下,利用非逻辑门,采用全加法器级联电路。利用2的补法实现了全加法器到全减法器的电路转换。

一般情况下,用非门逆变器对全加法器的减运算输入进行反运算。通过将这个被减数(非倒序输入)和减数(倒序输入)相加,FA电路的LSB(进位输入)为1,这意味着逻辑高,否则我们使用2的补码技术减去两个二进制数字。FA的输出是Diff位,如果我们将carry反转,我们就可以得到MSB的借位。实际上,我们可以设计出可以观察输出的电路。

Verilog代码

对于编码部分,首先,我们需要检查逻辑电路图的建模的结构方式。这可以使用AND门,半音,半音电路和逻辑门的组合构建逻辑图,以及逻辑门的组合,或者,而不是XOR门。与结构建模一样,我们向每个基本元素排列解释各种模块。在以下代码中,可以为每个大门定义不同的模块。

该模块适用于或门。

输入:a0,

输出:C0.

最后,我们将使用这些门将这些门将模块团联合成一个唯一的模块。为此,我们在这里使用模块的实例化。现在,一旦我们想复制一个完全的输入集,就可以使用此实例化。首先,我们设计一个半减法器,然后该模块用于实现完整的减法器。为了实现这一点,我们使用或门将O / PS组合起来的Bout变量。的完整减法器的verilog代码如下所示

模块or_gate(a0,b0,c0);

输入A0,B0;

输出c0;

分配C0 = A0 |B0;

终点

模块XOR_GATE(A1,B1,C1);

输入a1, b1;

输出C1;

赋值c1 = a1 ^ b1;

终点

module and_gate(a2, b2, c2);

输入A2,B2;

输出C2;

分配C2 = A2和B2;

终点

module not_gate(a3,b3);

输入a3;

输出B3;

分配b3 =〜a3;

终点

模块ALP_SUBTRACTOR(A4,B4,C4,D4);

输入A4,B4;

输出C4,D4;

x线;

xor_gate (a4, b4, c4);

and_gate u2(x, b4, d4);

not_gate u3(a4,x);

终点

模块Full_subtractor(A,B,Bin,D,Bout);

输入A、B、Bin;

输出D,Bout;

Wire P,Q,R;

半减子u4(A, B, p, q);

half_subtractor u5(p, Bin, D, r);

or_gate u6(q, r, Bout);

终点

使用4x1多路复用器的全减法器

可以通过两种补充方法执行减法。因此,我们需要利用用于反转1位的1-X型门,并将其包括一个携带位。的output of DIFFERENCE is similar to the output SUM in the full adder circuit however the BARROW o/p is not similar to the full adder’s carry output however it is inverted as well as complimented, like A – B = A + (-B) = A + two’s complement of B.

使用4x1多路复用器的设计如以下逻辑图所示。这种设计可以使用以下步骤完成。

- 在步骤1中,有两个输出如Sub和Bro。所以我们必须选择2个多路复用器。

- 在步骤2中,真值表可以与k -map一起实现

- 在步骤3中,可以选择这两个变量作为选择行。例如,B和C在这种情况下。

真值表

的全减法器的真理表电路使用4x1多路复用器包括以下内容

一个 |

B | C | 子 | 借 |

0 |

0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 |

1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 |

0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 |

1 | 1 | 1 | 1 |

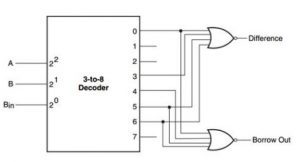

全减法器使用解码器

可以使用3-8解码器设计完整的减法器,可以使用有效的低输出来完成。让我们使用以下逻辑图来假设解码器功能。解码器包括3-8解码器中的三个输入。基于真相表,我们可以为差异和借用输出编写Minterms。

从上面的真相表,

对于真值表中的不同函数,分钟可以写成1、2、4、7,同理,对于借位,分钟可以写成1、2、3、7。3-8解码器包括3个输入以及8个输出像0到7个数字。

如果减法器的输入是000,那么输出' 0 '将是活跃的,如果输入是001,那么输出' 1 '将是活跃的。

现在减法器的输出可以从1、2、4和7中取出,并连接到与非门,然后输出将是差值。这些输出可以连接到其他非与逻辑门,在那里输出改变为借位。

例如,如果输入是001,则输出将是1表示它处于活动状态。所以输出处于高电平,输出可以从名为差异函数的NAND门获得,借用函数也变为高。因此,我们得到了首选的产出。最后,解码器就像一个完整的减法器一样。

的优点和缺点

的减法器的优点包括以下这些。

- 减法器的设计非常简单和工具

- DSP中的功率扣除(数字信号处理)

- 计算任务可以高速进行。

的减法器的缺点包括以下这些。

- 在半个减法器中,没有较早阶段接受借用的借阅。

- 减法器的速度可以通过电路中的延迟部分实现。

应用程序

某些全减值器的应用包括以下这些

- 这些通常用于计算机中的ALU(算术逻辑单元),以减去作为图形应用的CPU和GPU以降低电路难度。

- 减法器主要用于执行算术功能,如减法,电子计算器以及数字设备。

- 这些也适用于不同的微控制器用于算术减法,定时器和程序计数器(PC)

- 减法器用于处理器以计算表,地址等。

- 它对DSP和基于网络的系统也很有用。

- 这些主要用于在计算机内的ALU用于减去CPU和GPU的图形应用,以降低电路的复杂性。

- 这些主要用于执行算术功能,例如数字设备,计算器等减法。

- 这些减法器也适用于用于定时器,PC(程序计数器)和算术减法的各种微控制器

- 它们被用于处理器计算地址、表等。

- 像NAND和NOR这样的逻辑门的实现可以用任何全减法器逻辑电路来实现,因为这两个NOR和NAND门都被称为通用门。

根据上述信息,通过评估加法器,使用两个半减法器电路的完整减法器,以及其表格形式,可以注意到全减法器中的DOUT准确地与全加法器的SOUT。唯一的变化是(输入变量)在全减值器中补充。因此,可以通过在给出之前的补充I / P A之前将全吸收电路改变为全减法器逻辑门生成最后一个借用位输出(Bout)。

通过使用任何完整的减法器逻辑电路,可以实现使用使用NAND门和全减法器的全减法器,并且可以实现使用或门,因为NAND和NOR门都被视为通用门。这是一个问题,半音和全减法器之间有什么区别?

构建和测试全减法器电路